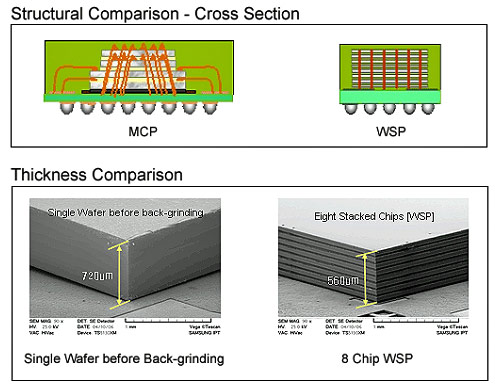

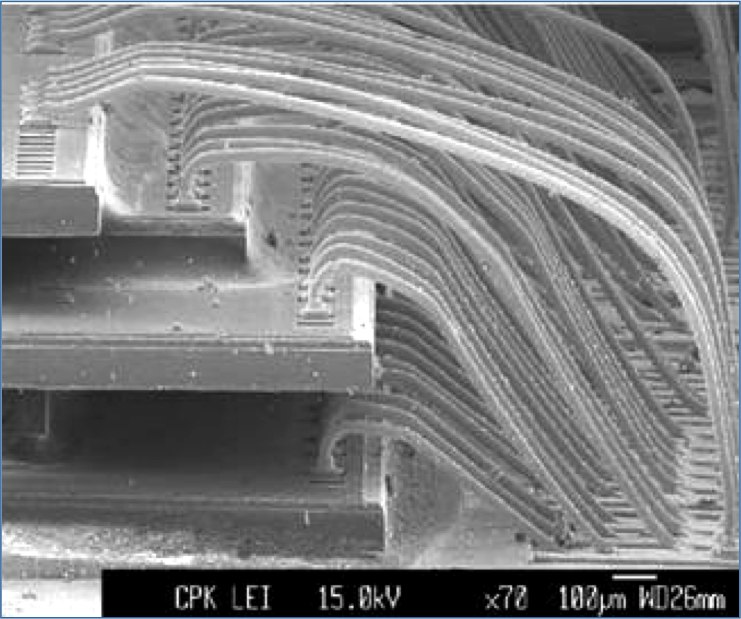

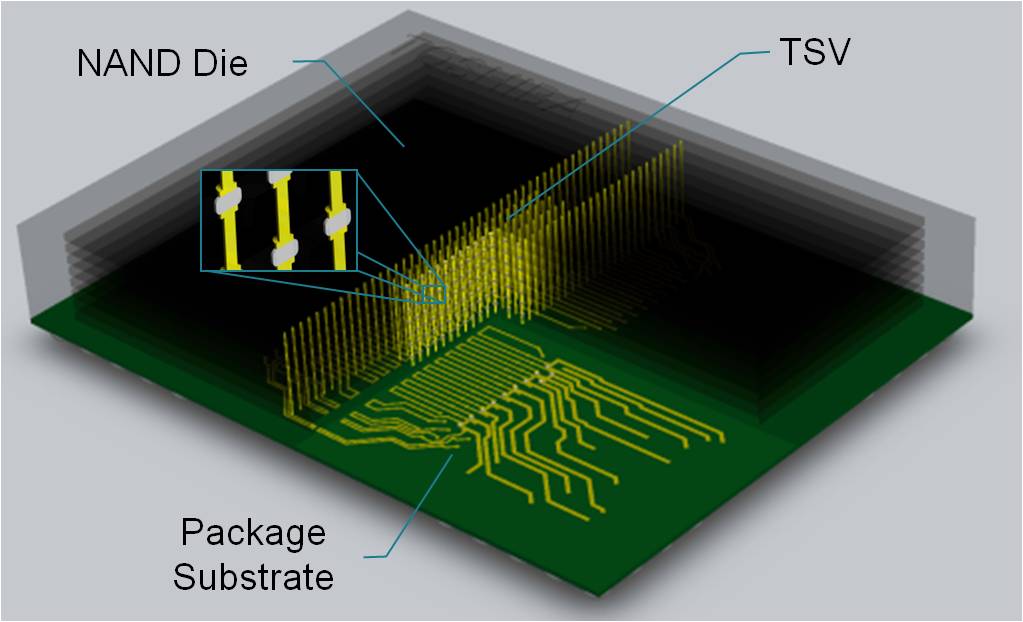

Figure 1 from Advances in Wire Bonding Technology for 3D Die Stacking and Fan Out Wafer Level Package | Semantic Scholar

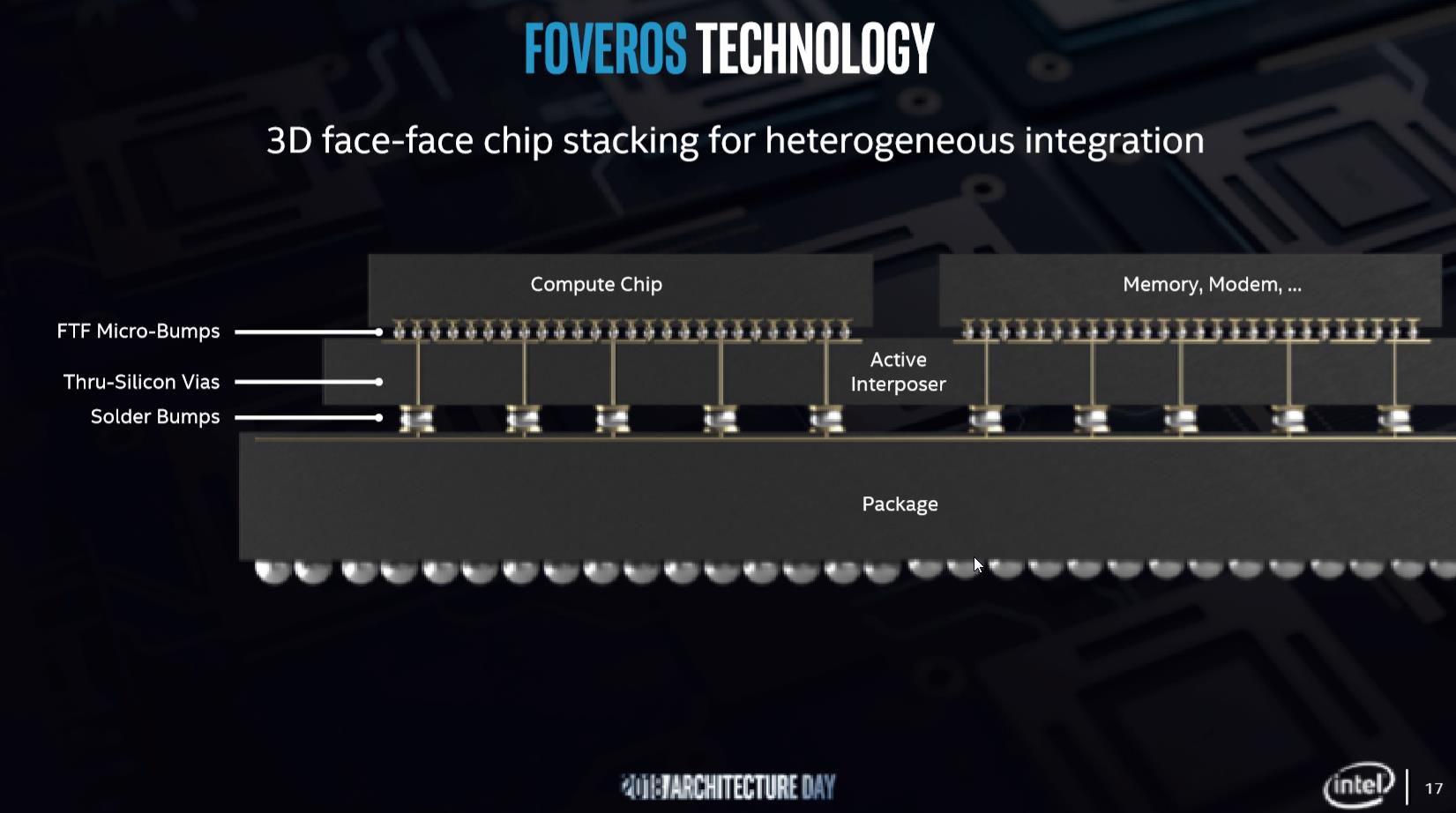

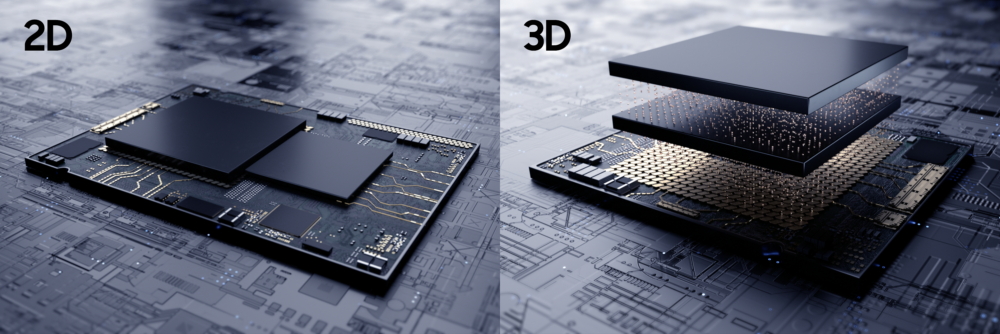

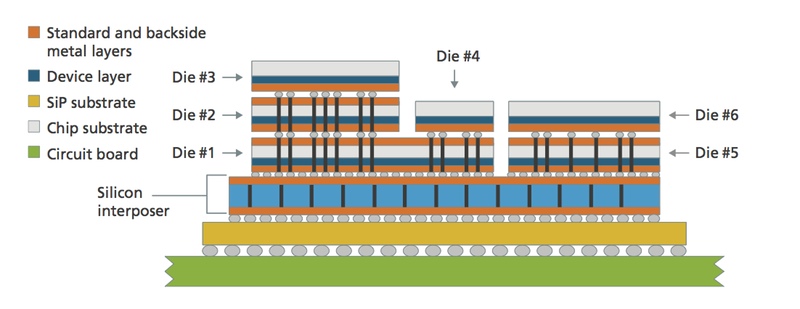

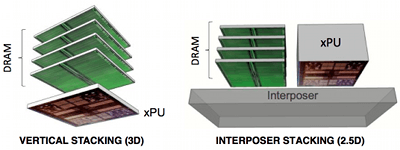

The different approaches in 3D-WLP integration: die stacking (left) and... | Download Scientific Diagram

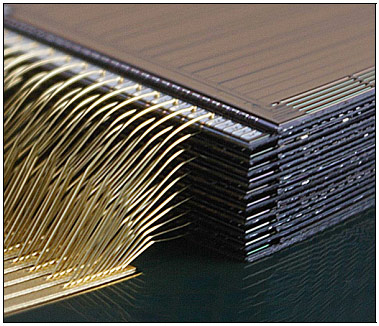

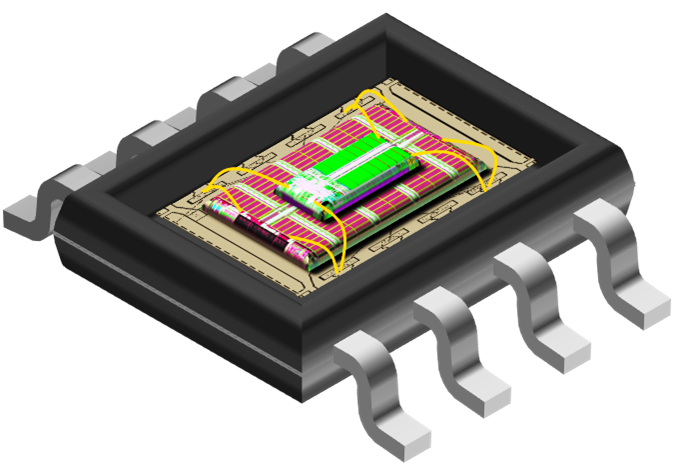

The SiP is formed with wire bonded stacked die inside the package. SMDs... | Download Scientific Diagram

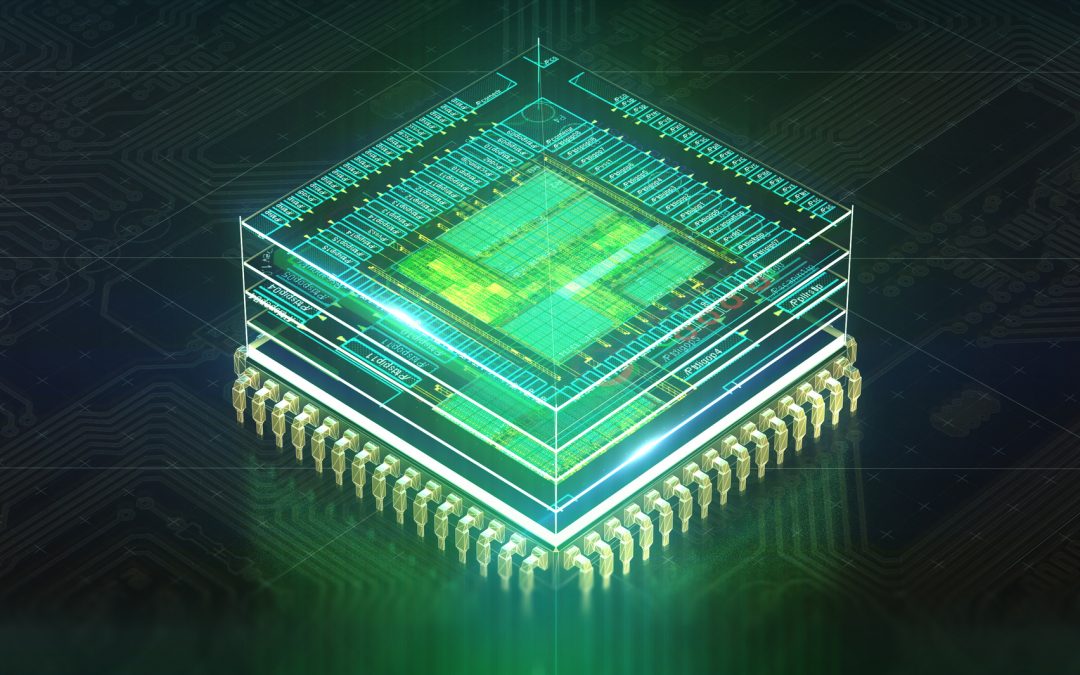

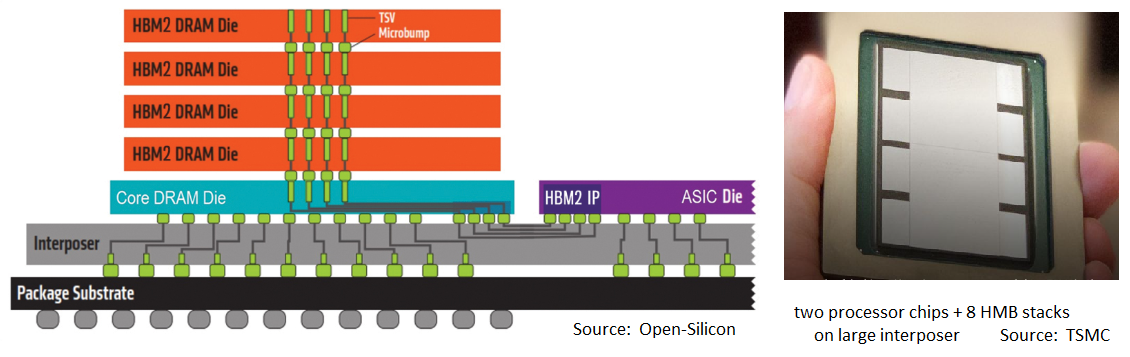

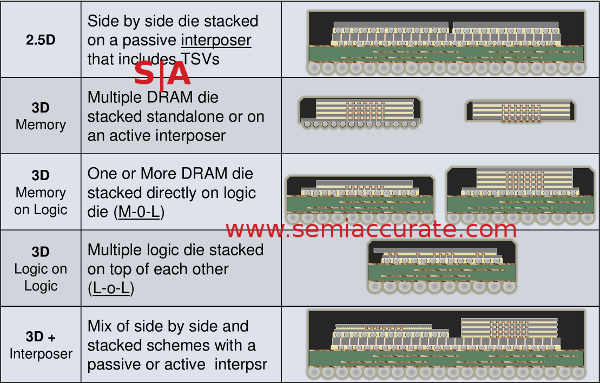

a) 2D enhanced: Side-by-side die stacked over interposer (2.5D) and... | Download Scientific Diagram

Technical Articles - How improved die-stacking technology reduces pin count, board footprint and system complexity - Winbond

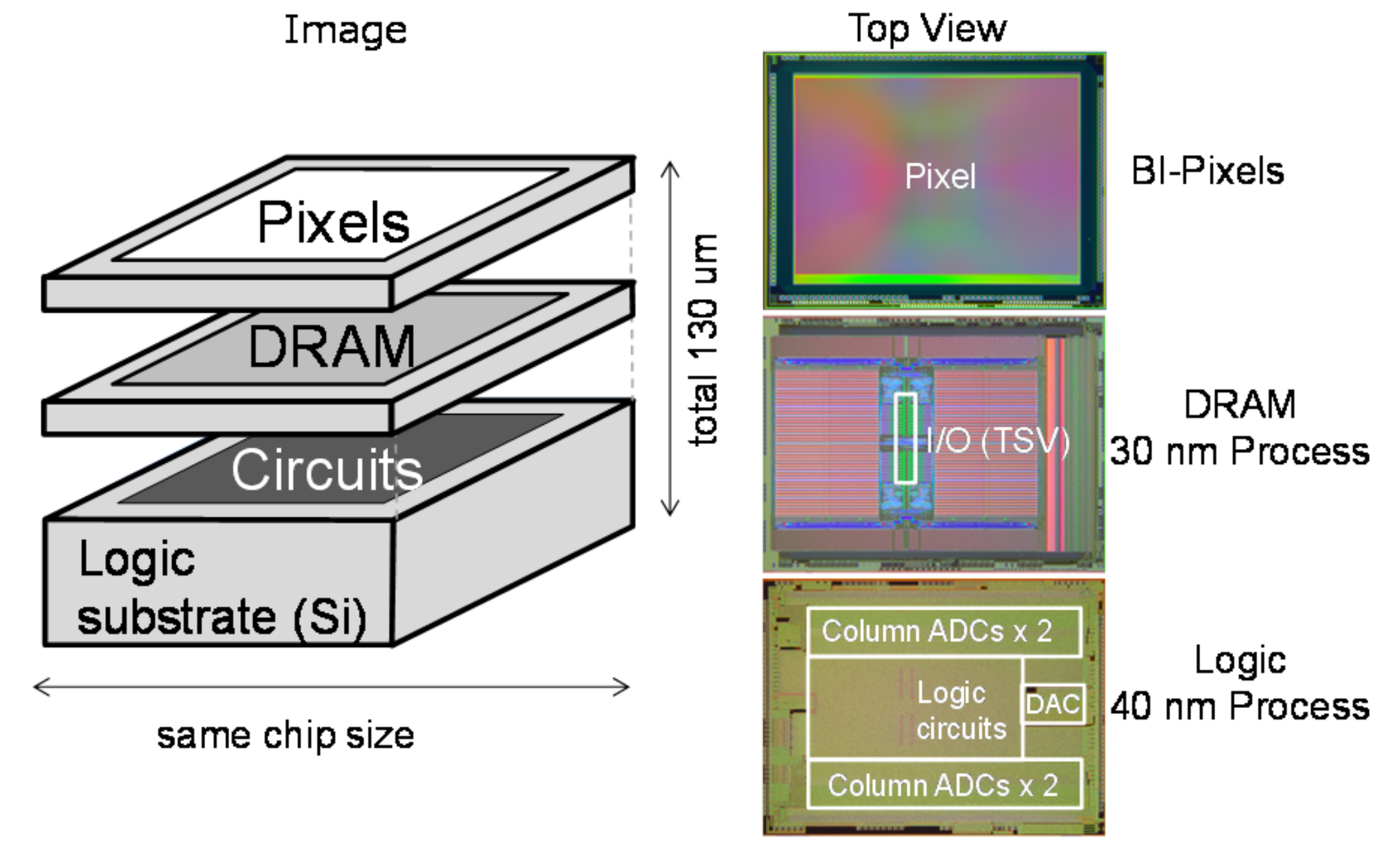

![PDF] Thermal Feasibility of Die-Stacked Processing in Memory | Semantic Scholar PDF] Thermal Feasibility of Die-Stacked Processing in Memory | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/a52945840b980adfef34466cb4186c7cda3b61e6/1-Figure1-1.png)